template<uint8_t N>

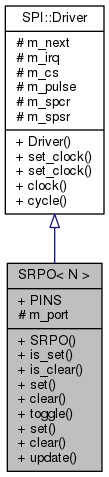

class SRPO< N >

N-Shift Register Parallel Output, 3-Wire SPI device driver. The shift registers (74HC595) may be cascaded for N*8-bit parallel output port (see circuit below). The pins are numbered from the first connect shift register (Q0..Q7) and updwards in the chain (Q8..Q15) and so on.

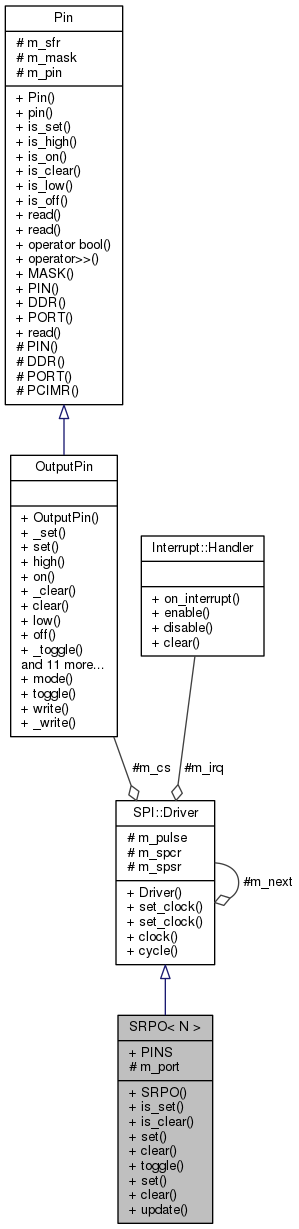

Circuit

74HC595 (VCC)

+----U----+ |

(Q1)----------------1-|Q1 VCC|-16-+

(Q2)----------------2-|Q2 Q0|-15------------(Q0)

(Q3)----------------3-|Q3 SER|-14------(MOSI/D11)

(Q4)----------------4-|Q4 /OE|-13-----------(GND)

(Q5)----------------5-|Q5 RCLK|-12--------(EN/D10)------+

(Q6)----------------6-|Q6 SCLK|-11-------(SCK/D13)----+ |

(Q7)----------------7-|Q7 /MR|-10-----------(VCC) | |

+-8-|GND Q7S|--9------------------+ | |

| +---------+ | | |

| 0.1uF | | |

(GND)-----||-------(VCC) | | |

| | | |

74HC595 | | | |

+----U----+ | | | |

(Q9)----------------1-|Q1 VCC|-16-+ | | |

(Q10)---------------2-|Q2 Q0|-15------------(Q8) | | |

(Q11)---------------3-|Q3 SER|-14------------------+ | |

(Q12)---------------4-|Q4 /OE|-13-----------(GND) | |

(Q13)---------------5-|Q5 RCLK|-12--------------------(-+

(Q14)---------------6-|Q6 SCLK|-11--------------------+ |

(Q15)---------------7-|Q7 /MR|-10-----------(VCC) | |

+-8-|GND Q7S|--9------------------+ | |

| +---------+ | | |

| 0.1uF | | |

(GND)-----||-------(VCC) | | |

| | | |

V V V V

Note

The shift registers will clock data for presented on the SPI bus (MOSI/SCK) but will not transfer to output register until the enable pulse is given (i.e. when addressed).

- Parameters

-

| [in] | N | number of shift registers (N * 8 output pins). |

Definition at line 74 of file SRPO.hh.