|

| | W5500 (const uint8_t *mac=NULL, Board::DigitalPin csn=Board::D10) |

| |

| void | addr (uint8_t ip[4], uint8_t subnet[4]) |

| |

| void | dns_addr (uint8_t ip[4]) |

| |

| bool | begin_P (const char *hostname, uint16_t timeout=500) |

| |

| bool | begin_P (str_P hostname, uint16_t timeout=500) |

| |

| bool | begin (uint8_t ip[4]=NULL, uint8_t subnet[4]=NULL, uint16_t timeout=500) |

| |

| int | bind (uint8_t ip[4], uint8_t subnet[4], uint8_t gateway[4]=NULL) |

| |

| Socket * | socket (Socket::Protocol proto, uint16_t port=0, uint8_t flag=0) |

| |

| bool | end () |

| |

|

| enum | {

MR_RST = 0x80,

MR_WOL = 0x20,

MR_PB = 0x10,

MR_PPPoE = 0x08,

MR_FARP = 0x02

} |

| |

| enum | { IR_CONFLICT = 0x80,

IR_UNREACH = 0x40,

IR_PPPoE = 0x20,

IR_MP = 0x10

} |

| |

| enum | { IMR_CONFLICT = 0x80,

IMR_UNREACH = 0x40,

IMR_PPPoE = 0x20,

IMR_MP = 0x10

} |

| |

| enum | {

SIR_S7_INT = 0x80,

SIR_S6_INT = 0x40,

SIR_S5_INT = 0x20,

SIR_S4_INT = 0x10,

SIR_S3_INT = 0x08,

SIR_S2_INT = 0x04,

SIR_S1_INT = 0x02,

SIR_S0_INT = 0x01

} |

| |

| enum | {

SIMR_S7_INT = 0x80,

SIMR_S6_INT = 0x40,

SIMR_S5_INT = 0x20,

SIMR_S4_INT = 0x10,

SIMR_S3_INT = 0x08,

SIMR_S2_INT = 0x04,

SIMR_S1_INT = 0x02,

SIMR_S0_INT = 0x01

} |

| |

| enum | {

MEM_SIZE_00K = 0x00,

MEM_SIZE_01K = 0x01,

MEM_SIZE_02K = 0x02,

MEM_SIZE_04K = 0x04,

MEM_SIZE_08K = 0x08,

MEM_SIZE_16K = 0x10

} |

| |

| enum | {

MR_FLAG_MASK = 0xe0,

MR_MULTIMF = 0x80,

MR_BCASTB = 0x40,

MR_NDMCMMB = 0x20,

MR_UCASTB = 0x10,

MR_PROTO_MASK = 0x0f,

MR_PROTO_CLOSED = 0x00,

MR_PROTO_TCP = 0x01,

MR_PROTO_UDP = 0x02,

MR_PROTO_IPRAW = 0x03,

MR_PROTO_MACRAW = 0x04

} |

| |

| enum | {

CR_OPEN = 0x01,

CR_LISTEN = 0x02,

CR_CONNECT = 0x04,

CR_DISCON = 0x08,

CR_CLOSE = 0x10,

CR_SEND = 0x20,

CR_SEND_MAC = 0x21,

CR_SEND_KEEP = 0x22,

CR_RECV = 0x40

} |

| |

| enum | {

IR_SEND_OK = 0x10,

IR_TIMEOUT = 0x08,

IR_RECV = 0x04,

IR_DISCON = 0x02,

IR_CON = 0x01

} |

| |

| enum | {

SR_CLOSED = 0x00,

SR_ARP = 0x01,

SR_INIT = 0x13,

SR_LISTEN = 0x14,

SR_SYNSENT = 0x15,

SR_SYNRECV = 0x16,

SR_ESTABLISHED = 0x17,

SR_FIN_WAIT = 0x18,

SR_CLOSING = 0x1A,

SR_TIME_WAIT = 0x1B,

SR_CLOSE_WAIT = 0x1C,

SR_LAST_ACK = 0x1D,

SR_UDP = 0x22,

SR_IPRAW = 0x32,

SR_MACRAW = 0x42,

SR_PPPoE = 0x5F

} |

| |

| enum | {

SPI_CP_BSB_CR = 0x00,

SPI_CP_BSB_SR = 0x08,

SPI_CP_BSB_TX = 0x10,

SPI_CP_BSB_RX = 0x18,

SPI_CP_RWB_RS = 0x00,

SPI_CP_RWB_WS = 0x04,

SPI_CP_OM_VDM = 0x00,

SPI_CP_OM_FD1 = 0x01,

SPI_CP_OM_FD2 = 0x02,

SPI_CP_OM_FD4 = 0x03

} |

| |

|

| void | write (uint16_t addr, uint8_t ctl, uint8_t data) |

| |

| void | write (uint16_t addr, uint8_t ctl, const void *buf, size_t len, bool progmem=false) |

| |

| void | write_P (uint16_t addr, uint8_t ctl, const void *buf, size_t len) |

| |

| uint8_t | read (uint16_t addr, uint8_t ctl) |

| |

| void | read (uint16_t addr, uint8_t ctl, void *buf, size_t len) |

| |

| void | issue (uint16_t addr, uint8_t ctl, uint8_t cmd) |

| |

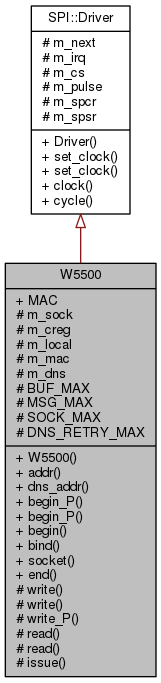

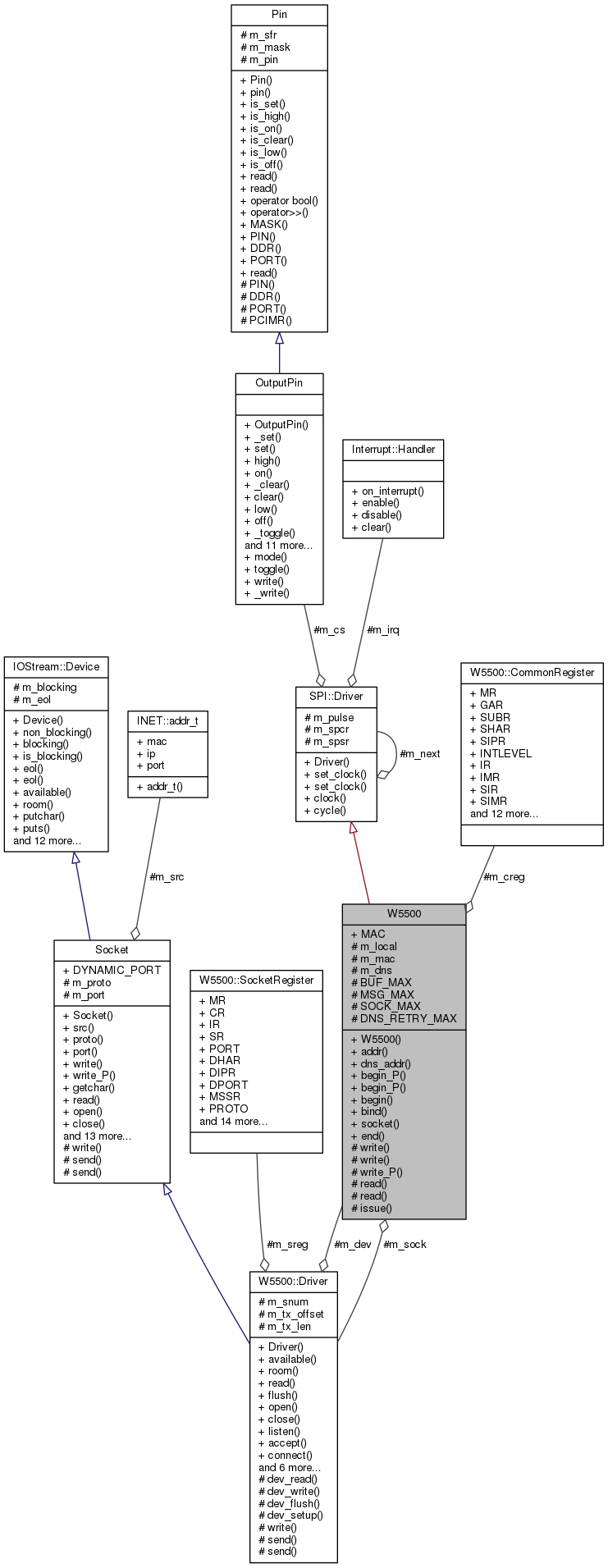

Cosa WIZnet W5500 device driver class. Provides an implementation of the Cosa Socket and Cosa IOStream::Device classes. A socket may be bound directly to a Cosa IOStream. The device internal transmitter buffer is used. The buffer is sent on flush (TCP/UDP) or when full (TCP). Integrated with Cosa INET/DHCP so that the ethernet controller may obtain a network address and information from a DHCP server.

Circuit

+------------+

(D10)--------------29-|CSN |

(D11)--------------28-|MOSI |

(D12)--------------27-|MISO |

(D13)--------------30-|SCK |

(D2)-----[ ]-------56-|IRQ |

+------------+

References

- W5500 Datasheet Version 1.0.6, December 30, 2014, http://wizwiki.net/wiki/lib/exe/fetch.php?media=products:w5500:w5500_ds_v106e_141230.pdf

- W5500 Application Note 1.1 April 09, 2014, http://wizwiki.net/wiki/lib/exe/fetch.php?media=products:w5500:w5500_ap_ipraw_v110e.pdf

Definition at line 57 of file W5500.hh.